## Master Project Heat management in Silicon spin qubits networks

Worldwide effort is ongoing to build a quantum processor. Among candidates as physical units carrying the quantum information (the qubits), electron spins in solid state devices have made their marks. In these systems, the information is encoded on a single electron spin, trapped in a quantum dot. Efficient single, two and four qubit gates, building blocks of a future quantum processor, have recently been demonstrated in various solid states devices [1-4].

This master project, possibly followed by a PhD thesis, will focus on fundamental questions concerning thermal aspects in these novel quantum devices. For example: What is the amount of heat generated by the high-frequency electrical signals employed for qubit manipulation? How does it impact the qubit operations fidelity? Can we envision schemes to counteract heating effects?

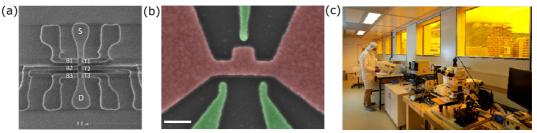

This master thesis will aim at the experimental realization of primary electronic thermometers embedded in a semiconductor qubit architecture. The devices will generally consist of gate-defined multiple quantum-dot structures (see e.g. Fig.1a), in which one of the quantum dots is used as a local, non-galvanic thermometer.

Two types of systems will be available: i) quantum dot devices issued from the CMOS fab line of Leti (see Fig.1a); ii) quantum-dot devices fabricated from strained Ge/SiGe heterostructures (Fig.1b). The master student will carry out low-temperature experiments involving high-frequency charge detection techniques. This project is part of a large research effort between CEA and CNRS in Grenoble for the development of quantum computing based on CMOS technology see: http://www.quantumsilicon-grenoble.eu.

The candidate should show a strong interest in experimental research and have a solid background in solid-state physics and quantum mechanics.

Fig1: a) Multi-quantum dots device from the LETI CMOS fabrication line. b) Ge/SiGe device fabricated in the CEA cleanroom. C) Clean-room facilities at the CEA.

**References :** [1] Petta et al. Science **309**, 2180–2184 (2005) [2] Maurand et al., Nature Commun., **7**, 13575 (2016) [3] Hendrickx et al. Nature **577**, 487-491 (2020) [4] Hendrickx et al., <u>arXiv:2009.04268</u> (2020)

## **APPLY NOW!**

To apply for this position, send your application (including CV) by e-mail to: silvano.defranceschi@cea.fr Lab website: http://lateqs.fr

French Commission for Atomic Energy and Alternative Energies Interdisciplinary Research Institute of Grenoble Quantum Photonics, Electronics and Engineering Laboratory 17 av. des Martyrs – 38054 Grenoble cedex 9 – France